パワーグリッドがACであることには多くの正当な理由があります。しかし、ほぼすべての装置が動作するのにDC電源を必要とします。これはあらゆる場所でAC-DC電源が使用されていることを意味し、環境意識が高まりエネルギーコストが上昇している時代において、運用コストを抑えてエネルギーを賢く使用するには、電源の効率がきわめて重要です。

簡単に言うと、効率とは入力電力と出力電力の比率のことです。ただし、入力力率(PF)を考慮する必要があります。これは電源を含むあらゆるAC電源装置における有効(真の)電力と合計(皮相)電力の比率です。

純抵抗負荷の場合、PFは1.00 (unity)になりますが、無効負荷では皮相電力が上昇するにつれてPFが低下し、効率の低下につながります。PFが1未満になるのは、電圧と電流の位相のずれ、大きな高調波成分、または電流波形の歪みが原因です。これはスイッチモード電源(SMPS)などの不連続性電子負荷でよく見られます。

力率補正

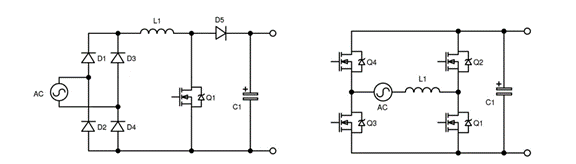

低いPFが効率に及ぼす影響を考慮すると、電力レベルが70 Wを超える場合、法律によりPFを1に近い値に補正する回路を組み込むことが、設計者に義務付けられています。多くの場合に、アクティブPF補正(PFC)は、整流された主電源を高いDCレベルに変換する昇圧コンバータを採用しています。このレールはパルス幅変調(PWM)や他の手法を使って安定化されます。

このアプローチは一般的に良い結果が得られ、導入も簡単です。しかし、難易度の高い「80PLUS Titanium規格」のような最新の効率要件では、広い動作電力範囲にわたる効率が規定されており、半負荷時のピーク効率96%が要求されます。これが意味するのは、後続のPWM DC-DCがさらに2%損失するため、ライン整流とPFCステージで98%を達成する必要があるということです。ブリッジ整流器のダイオード内で損失が発生するため、この目標を達成するのは非常に困難です。

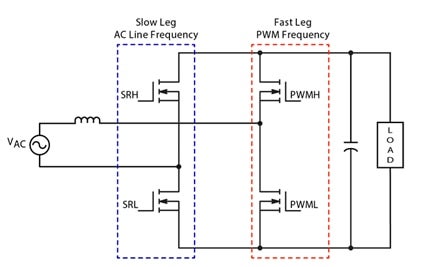

昇圧ダイオードを同期整流器に置き換えると効果的であり、2個のライン整流器ダイオードを同様に置き換えると、さらに効率が向上します。このトポロジはトーテムポールPFC (TPPFC)と呼ばれ、理論上、理想的なインダクタと完璧なスイッチを使用すれば、効率は100%に近づきます。シリコンMOSFETは優れた性能を発揮しますが、ワイドバンドギャップ(WBG)デバイスではさらに「理想的な」性能に近づきます。

図1:簡易トーテムポールPFCトポロジ

損失への対処

設計者が磁気部品のサイズを小型化するために周波数を高くすると、スイッチングデバイスの動的損失も増加します。シリコンMOSFETでは、これらの損失が大きくなる可能性があるため、特にTPPFCアプリケーションでは、設計者はシリコンカーバイド(SiC)や窒化ガリウム(GaN)などのWBG材料に目を向けています。

臨界導通モード(CrM)は一般に、最大数百ワットの電力レベルでのTPPFC設計に対して推奨されるアプローチであり、効率とEMI性能のバランスを図ります。キロワット設計では、連続導通モード(CCM)によりスイッチ内の実効電流がさらに減少し、導通損失が低減されます。

図2:代表的なPFC回路:従来式ブースト(左) および ブリッジレストーテムポール(右)

CrMであっても、軽負荷時には効率が10%近く低下することがあり、これは「80PlusTitanium」を達成するための障害となります。最大周波数をクランプ(フォールドバック)して、軽負荷時に回路を強制的にDCMに移行させ、ピーク電流を大幅に低減します。

設計の複雑さを克服

4個のアクティブデバイスを同期して駆動し、インダクタのゼロ電流クロスを検出してCrMを強制する必要があるため、TPPFCの設計は簡単とは言えません。さらに、回路は高い力率を維持し、出力を調整するPWM信号を生成しながら、DCMへの移行、DCMからの移行を切り替えなければなりません。同時に、回路保護(過電流や過電圧などに対する)も提供する必要があります。

これらの複雑な動作に対処する明白な方法は、制御アルゴリズムにマイクロコントローラ(MCU)を導入することです。しかし、これにはコードの生成とデバッグが必要であり、設計に多大な労力とリスクを伴います。

コーディング不要のCrMベースTPPFC

しかし、完全に統合されたTPPFC制御ソリューションを使用すれば、時間のかかるコーディングをなくすことができます。これらのデバイスは、MCUと関連のコードを実装する必要がないため、高性能、設計時間の短縮、設計リスクの軽減など、いくつもの利点があります。

このタイプのデバイスの好例は、一定オン時間CrMで動作するオンセミのNCP1680ミックスドシグナルTPPFCコントローラです。このコントローラにより、広い負荷範囲にわたって優れた効率を達成できます。この統合デバイスは、軽負荷時の周波数フォールドバックでの「バレースイッチング」機能を備えており、最小電圧でスイッチングすることで効率を向上させます。デジタル電圧制御ループが内部で補正され、負荷の全範囲にわたって性能が最適化されますが、簡素な設計プロセスはそのままです。

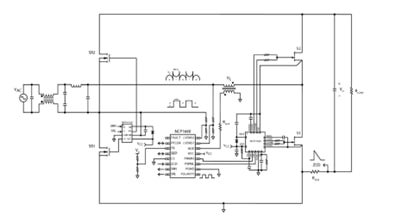

図3:NCP1680ミックスドシグナルTPPFCコントローラ

この革新的なTPPFCコントローラは、電流検出のための斬新な低損失アプローチを内蔵しており、サイクル単位の電流制限により、外付けホール効果センサなしで十分な保護を提供します。これによって、複雑さ、サイズ、コストを低減します。

図4:NCP1680の代表的なアプリケーション回路図

制御アルゴリズム全一式がICに組み込まれているため、設計者は費用効果の大きい価格帯で高性能を発揮する、低リスクのテスト済みソリューションを入手できます。