# **SiC JFET Division**

Is Now Part of

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

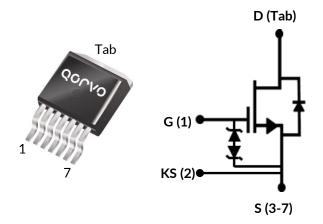

# UF4C120070B7S

| Part Number   | Package               | Marking       |

|---------------|-----------------------|---------------|

| UF4C120070B7S | D <sup>2</sup> PAK-7L | UF4C120070B7S |

# Silicon Carbide (SiC) Cascode JFET -EliteSiC, Power N-Channel, D2PAK-7L, 1200 V, 72 mohm

Rev B, January 2025

## Description

The UF4C120070B7S is a 1200V,  $72m\Omega$  G4 SiC FET. It is based on a unique 'cascode' circuit configuration, in which a normally-on SiC JFET is co-packaged with a Si MOSFET to produce a normally-off SiC FET device. The device's standard gate-drive characteristics allows use of off-the-shelf gate drivers hence requiring minimal re-design when replacing Si IGBTs, Si superjunction devices or SiC MOSFETs. Available in the space-saving D²PAK-7L package which enables automated assembly, this device exhibits ultra-low gate charge and exceptional reverse recovery characteristics, making it ideal for switching inductive loads and any application requiring standard gate drive.

#### **Features**

- On-resistance R<sub>DS(on)</sub>: 72mΩ (typ)

- Operating temperature: 175°C (max)

- Excellent reverse recovery: Q<sub>rr</sub> = 101nC

- ◆ Low body diode V<sub>FSD</sub>: 1.43V

- Low gate charge: Q<sub>G</sub> = 37.8nC

- Threshold voltage V<sub>G(th)</sub>: 4.8V (typ) allowing 0 to 15V drive

- Low intrinsic capacitance

- ESD protected: HBM class 2 and CDM class C3

- D<sup>2</sup>PAK-7L package for faster switching, clean gate waveforms

## Typical applications

- EV charging

- PV inverters

- Switch mode power supplies

- Power factor correction modules

- Induction heating

# **Maximum Ratings**

| Parameter                                   | Symbol                                                                                                                                                  | Test Conditions               | Value      | Units |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------|-------|

| Drain-source voltage                        | $V_{DS}$                                                                                                                                                |                               | 1200       | V     |

| Gate-source voltage                         | V                                                                                                                                                       | DC                            | -20 to +20 | V     |

| Gate-source voltage                         | $V_{GS} = \begin{array}{c} DC \\ AC (f > 1Hz) \\ T_{C} = 25^{\circ}C \\ \hline T_{C} = 100^{\circ}C \\ \hline I_{DM} \\ E_{AS} \\ dv/dt \\ \end{array}$ | -25 to +25                    | V          |       |

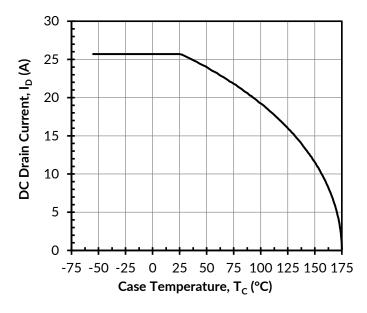

| Continuous drain current <sup>1</sup>       | I_                                                                                                                                                      | T <sub>C</sub> = 25°C         | 25.7       | Α     |

| Continuous drain current                    | 'D                                                                                                                                                      | T <sub>C</sub> = 100°C        | 19.2       | Α     |

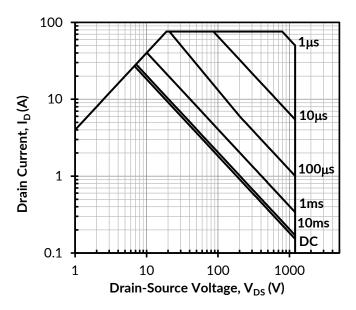

| Pulsed drain current <sup>2</sup>           | I <sub>DM</sub>                                                                                                                                         | T <sub>C</sub> = 25°C         | 76         | Α     |

| Single pulsed avalanche energy <sup>3</sup> | E <sub>AS</sub>                                                                                                                                         | L=15mH, I <sub>AS</sub> =2.2A | 36         | mJ    |

| SiC FET dv/dt ruggedness                    | dv/dt                                                                                                                                                   | V <sub>DS</sub> ≤ 800V        | 200        | V/ns  |

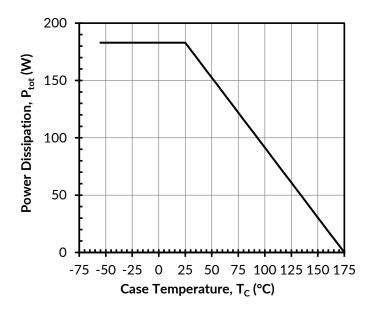

| Power dissipation                           | P <sub>tot</sub>                                                                                                                                        | T <sub>C</sub> = 25°C         | 183        | W     |

| Maximum junction temperature                | $T_{J,max}$                                                                                                                                             |                               | 175        | °C    |

| Operating and storage temperature           | $T_J, T_{STG}$                                                                                                                                          |                               | -55 to 175 | °C    |

| Reflow soldering Temperature                | $T_{solder}$                                                                                                                                            | reflow MSL 1                  | 245        | °C    |

- 1. Limited by  $T_{J,max}$

- 2. Pulse width  $t_p$  limited by  $T_{J,max}$

- 3. Starting  $T_J = 25$ °C

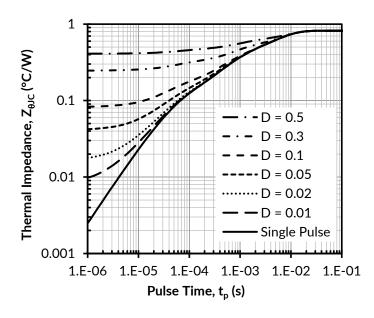

## **Thermal Characteristics**

| Parameter                            | Symbol Test Conditions |                 | Value |      |      | Units  |

|--------------------------------------|------------------------|-----------------|-------|------|------|--------|

| Parameter                            | Symbol                 | rest Conditions | Min   | Тур  | Max  | Offits |

| Thermal resistance, junction-to-case | $R_{\theta JC}$        |                 |       | 0.63 | 0.82 | °C/W   |

# Electrical Characteristics ( $T_J = +25^{\circ}$ C unless otherwise specified) Typical Performance - Static

| Parameter                      | Symbol Test Conditions |                                            | Value |     |     | Units |

|--------------------------------|------------------------|--------------------------------------------|-------|-----|-----|-------|

| Parameter                      | Symbol                 | Test Conditions                            | Min   | Тур | Max | Units |

| Drain-source breakdown voltage | BV <sub>DS</sub>       | $V_{GS}$ =0V, $I_D$ =1mA                   | 1200  |     |     | V     |

|                                |                        | V <sub>DS</sub> =1200V,                    |       | 0.4 | 10  |       |

| Total drain lookaga surrant    |                        | $V_{GS}=0V, T_J=25$ °C                     |       | 0.4 | 18  |       |

| Total drain leakage current    | I <sub>DSS</sub>       | V <sub>DS</sub> =1200V,                    |       | 40  |     | - μΑ  |

|                                |                        | V <sub>GS</sub> =0V, T <sub>J</sub> =175°C |       | 10  |     |       |

| Tatal cata leakage auguset     |                        | V <sub>DS</sub> =0V, T <sub>J</sub> =25°C, |       | ,   | 20  |       |

| Total gate leakage current     | I <sub>GSS</sub>       | V <sub>GS</sub> =-20V / +20V               |       | 6   |     | μΑ    |

|                                |                        | V <sub>GS</sub> =12V, I <sub>D</sub> =20A, |       | 70  | 91  |       |

|                                |                        | T <sub>J</sub> =25°C                       |       | 72  |     |       |

| Drain-source on-resistance     | D                      | V <sub>GS</sub> =12V, I <sub>D</sub> =20A, |       | 140 |     | mΩ    |

| Drain-source on-resistance     | R <sub>DS(on)</sub>    | T <sub>J</sub> =125°C                      |       | 140 |     |       |

|                                |                        | $V_{GS}$ =12V, $I_{D}$ =20A,               |       | 107 |     |       |

|                                |                        | <sub>Т,</sub> =175°С                       |       | 197 |     |       |

| Gate threshold voltage         | $V_{G(th)}$            | $V_{DS}$ =5V, $I_{D}$ =10mA                | 4     | 4.8 | 6   | V     |

| Gate resistance                | $R_{G}$                | f=1MHz, open drain                         |       | 4.5 |     | Ω     |

# Typical Performance - Reverse Diode

| Parameter                                     | Symbol Test Conditions – |                                                                     | Value |      |      | Units  |  |

|-----------------------------------------------|--------------------------|---------------------------------------------------------------------|-------|------|------|--------|--|

| rarameter                                     | Зуппрог                  | Test Conditions                                                     | Min   | Тур  | Max  | Offics |  |

| Diode continuous forward current <sup>1</sup> | I <sub>S</sub>           | T <sub>C</sub> =25°C                                                |       |      | 25.7 | Α      |  |

| Diode pulse current <sup>2</sup>              | $I_{S,pulse}$            | T <sub>C</sub> =25°C                                                |       |      | 76   | Α      |  |

|                                               | V                        | $V_{GS}$ =0V, $I_{S}$ =10A, $T_{J}$ =25°C                           |       | 1.43 | 1.64 | .,     |  |

| Forward voltage                               | V <sub>FSD</sub>         | $V_{GS}$ =0V, $I_{S}$ =10A, $T_{J}$ =175°C                          |       | 2.38 |      | V      |  |

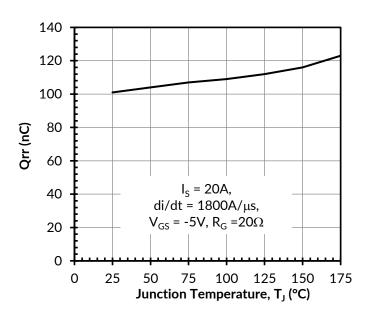

| Reverse recovery charge                       | Q <sub>rr</sub>          | $V_{DS}$ =800V, $I_{S}$ =20A, $V_{GS}$ =-5V, $R_{G}$ =20 $\Omega$ , |       | 101  |      | nC     |  |

| Reverse recovery time                         | t <sub>rr</sub>          | di/dt=1800A/μs,<br>Τ <sub>J</sub> =25°C                             |       | 11   |      | ns     |  |

| Reverse recovery charge                       | $Q_{rr}$                 | $V_{DS}$ =800V, $I_{S}$ =20A, $V_{GS}$ =-5V, $R_{G}$ =20 $\Omega$ , |       | 116  |      | nC     |  |

| Reverse recovery time                         | t <sub>rr</sub>          | di/dt=1800A/μs,<br>Τ <sub>J</sub> =150°C                            |       | 11   |      | ns     |  |

# Typical Performance - Dynamic

| D                                               | 6 1 1                | T 16 12                                                                                                                                                                  | Value |      |     | 11.2    |

|-------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----|---------|

| Parameter                                       | Symbol               | Test Conditions                                                                                                                                                          | Min   | Тур  | Max | - Units |

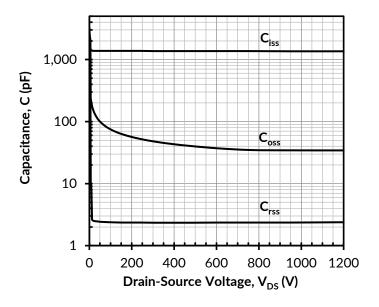

| Input capacitance                               | C <sub>iss</sub>     | - V <sub>DS</sub> =800V, V <sub>GS</sub> =0V -                                                                                                                           |       | 1370 |     |         |

| Output capacitance                              | $C_{oss}$            | f=100kHz                                                                                                                                                                 |       | 35   |     | pF      |

| Reverse transfer capacitance                    | $C_{rss}$            | 1-100KHZ                                                                                                                                                                 |       | 2    |     |         |

| Effective output capacitance, energy related    | C <sub>oss(er)</sub> | $V_{DS}$ =0V to 800V,<br>$V_{GS}$ =0V                                                                                                                                    |       | 42   |     | pF      |

| Effective output capacitance, time related      | C <sub>oss(tr)</sub> | V <sub>DS</sub> =0V to 800V,<br>V <sub>GS</sub> =0V                                                                                                                      |       | 71   |     | pF      |

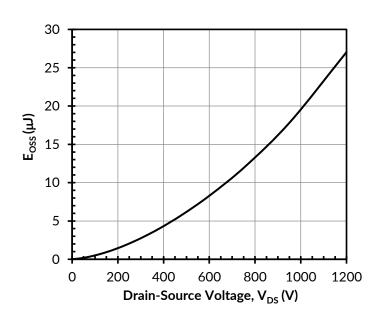

| C <sub>OSS</sub> stored energy                  | E <sub>oss</sub>     | V <sub>DS</sub> =800V, V <sub>GS</sub> =0V                                                                                                                               |       | 13.4 |     | μЈ      |

| Total gate charge                               | $Q_{G}$              | V <sub>DS</sub> =800V, I <sub>D</sub> =20A,                                                                                                                              |       | 37.8 |     |         |

| Gate-drain charge                               | $Q_{GD}$             | $V_{DS}=000V$ , $I_D=20\Delta$ , $V_{GS}=0V$ to 15V                                                                                                                      |       | 9.5  |     | nC      |

| Gate-source charge                              | $Q_GS$               | V GS-0V 10 13 V                                                                                                                                                          |       | 10   |     |         |

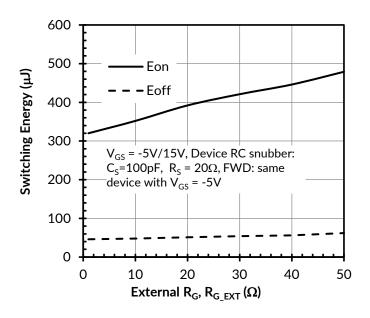

| Turn-on delay time                              | $t_{d(on)}$          |                                                                                                                                                                          |       | 20   |     |         |

| Rise time                                       | t <sub>r</sub>       | Notes 4 and 5, $V_{DS}=800V, I_{D}=20A, Gate$ $Driver=-5V \text{ to } +15V,$ $R_{G_{ON}}=10\Omega, R_{G_{OFF}}=50\Omega,$ inductive Load, $FWD: \text{same device with}$ |       | 32   |     | ns      |

| Turn-off delay time                             | t <sub>d(off)</sub>  |                                                                                                                                                                          |       | 57   |     |         |

| Fall time                                       | t <sub>f</sub>       |                                                                                                                                                                          |       | 12   |     |         |

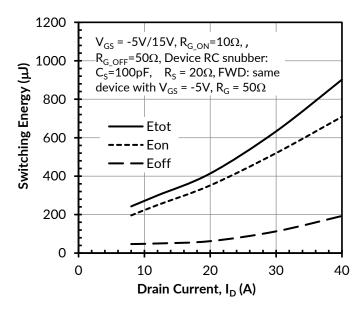

| Turn-on energy including R <sub>S</sub> energy  | E <sub>ON</sub>      |                                                                                                                                                                          |       | 352  |     | μ       |

| Turn-off energy including R <sub>S</sub> energy | E <sub>OFF</sub>     | $V_{GS}$ =-5V and $R_{G\_OFF}$ =50 $\Omega$ ,                                                                                                                            |       | 62   |     |         |

| Total switching energy                          | E <sub>TOTAL</sub>   | Device Snubber:                                                                                                                                                          |       | 414  |     |         |

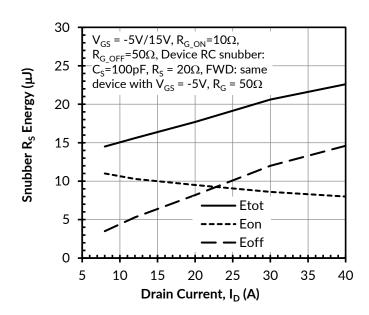

| Snubber R <sub>S</sub> energy during turn-on    | E <sub>RS_ON</sub>   | Cs=100pF,Rs=20Ω<br>T <sub>1</sub> =25°C                                                                                                                                  |       | 10   |     |         |

| Snubber R <sub>S</sub> energy during turn-off   | E <sub>RS_OFF</sub>  | ]                                                                                                                                                                        |       | 8    |     |         |

| Turn-on delay time                              | $t_{d(on)}$          | Notes 4 and 5,                                                                                                                                                           |       | 24   |     |         |

| Rise time                                       | t <sub>r</sub>       | V <sub>DS</sub> =800V, I <sub>D</sub> =20A, Gate                                                                                                                         |       | 33   |     | nc      |

| Turn-off delay time                             | $t_{d(off)}$         | Driver=-5V to +15V,                                                                                                                                                      |       | 63   |     | – ns    |

| Fall time                                       | $t_f$                | $R_{G_ON}=10\Omega$ , $R_{G_OFF}=50\Omega$ , inductive Load,                                                                                                             |       | 13   |     |         |

| Turn-on energy including R <sub>S</sub> energy  | E <sub>ON</sub>      | FWD: same device with                                                                                                                                                    |       | 396  |     |         |

| Turn-off energy including R <sub>S</sub> energy | E <sub>OFF</sub>     | $V_{GS}$ =-5V and $R_{G\_OFF}$ =50 $\Omega$ ,                                                                                                                            |       | 81   |     |         |

| Total switching energy                          | E <sub>TOTAL</sub>   | Device Snubber:                                                                                                                                                          |       | 477  |     | μJ      |

| Snubber R <sub>S</sub> energy during turn-on    | E <sub>RS_ON</sub>   | Cs=100pF,Rs=20Ω<br>T <sub>1</sub> =150°C                                                                                                                                 |       | 5    |     |         |

| Snubber R <sub>S</sub> energy during turn-off   | $E_{RS\_OFF}$        | 1 <sub>J</sub> =130 C                                                                                                                                                    |       | 12   |     |         |

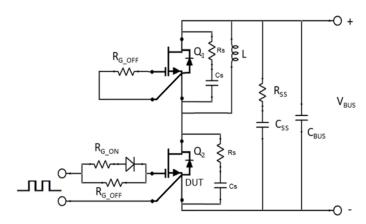

<sup>4.</sup> Measured with the half-bridge mode switching test circuit in Figure 26.

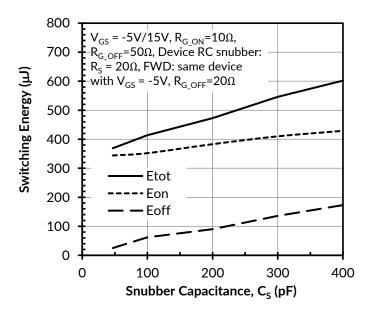

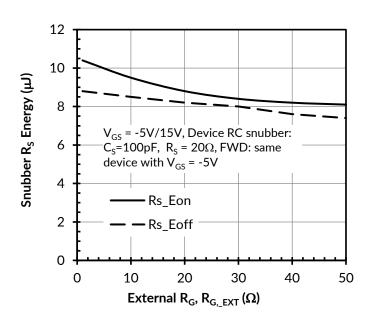

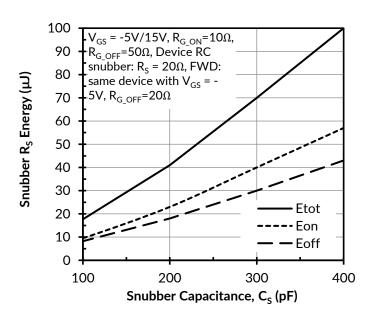

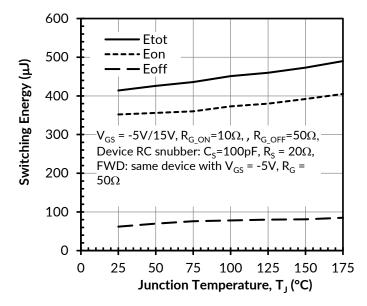

<sup>5.</sup> In this datasheet, all the switching energies (turn-on energy, turn-off energy and total energy) presented in the tables and Figures include the device RC snubber energy losses.

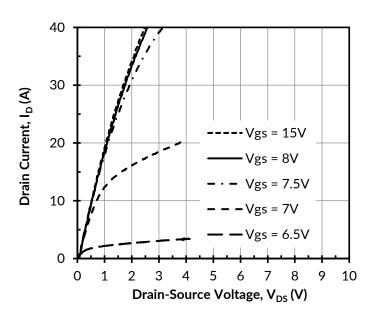

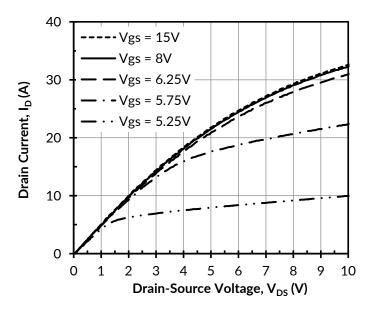

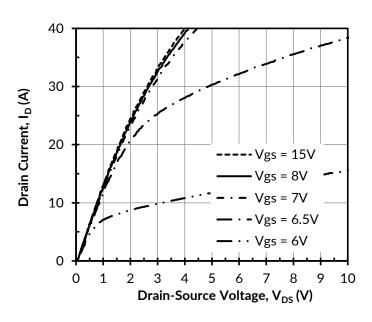

## **Typical Performance Diagrams**

Figure 1. Typical output characteristics at  $T_J$  = - 55°C, tp < 250 $\mu$ s

Figure 3. Typical output characteristics at  $T_J$  = 175°C, tp < 250 $\mu$ s

Figure 2. Typical output characteristics at  $T_J$  = 25°C, tp < 250 $\mu$ s

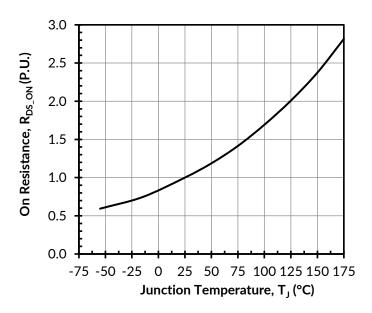

Figure 4. Normalized on-resistance vs. temperature at  $V_{GS}$  = 12V and  $I_D$  = 20A

30 Tj = -55°C 25 Tj = 25°C Tj = 175°C Drain Current, I<sub>D</sub> (A) 20 15 10 5 0 5 0 1 3 6 9 10 2 Gate-Source Voltage,  $V_{GS}$  (V)

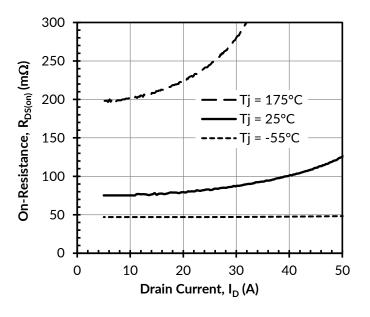

Figure 5. Typical drain-source on-resistances at  $V_{\text{GS}}$  = 12V

Figure 6. Typical transfer characteristics at  $V_{DS}$  = 5V

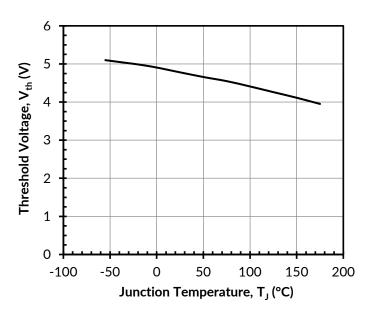

Figure 7. Threshold voltage vs. junction temperature at  $V_{DS}$  = 5V and  $I_{D}$  = 10mA

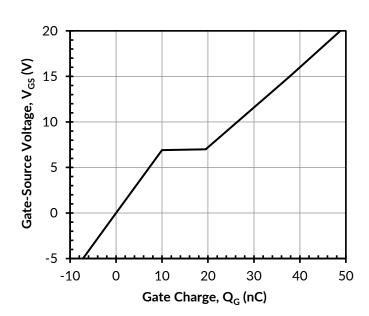

Figure 8. Typical gate charge at  $I_D$  = 20A and  $V_{DS}$ =800V

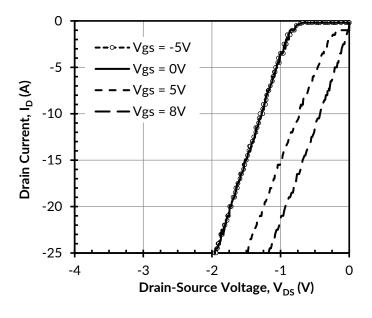

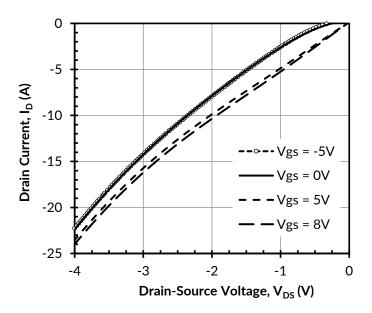

0 --- Vgs = - 5V Vgs = 0V -5 <del>-</del> Vgs = 5V Drain Current, I<sub>D</sub> (A) **-** Vgs = 8V -10 -15 -20 -25 -3 -1 -2 0 Drain-Source Voltage, V<sub>DS</sub> (V)

Figure 9. 3rd quadrant characteristics at  $T_J = -55$ °C

Figure 10. 3rd quadrant characteristics at  $T_J = 25$ °C

Figure 11. 3rd quadrant characteristics at  $T_J = 175$ °C

Figure 12. Typical stored energy in  $C_{OSS}$  at  $V_{GS} = 0V$

Figure 13. Typical capacitances at f = 100kHz and  $V_{GS}$  = 0V

Figure 14. DC drain current derating

Figure 15. Total power dissipation

Figure 16. Maximum transient thermal impedance

Figure 17. Safe operation area at  $T_C$  = 25°C, D = 0, Parameter  $t_p$

Figure 19. Clamped inductive switching energy vs. Drain Current at  $V_{DS}$  = 800V and  $T_J$  = 25°C

Figure 18. Reverse recovery charge Qrr vs. junction temperature at  $V_{DS}$  = 800V

Figure 20. RC snubber energy loss vs. Drain Current at  $V_{DS} = 800V$ ,  $I_D = 20A$ , and  $T_J = 25$ °C

Figure 21. Clamped inductive switching energies vs.  $R_{G,EXT}$  at  $V_{DS}$  = 800V,  $I_{D}$  = 20A, and  $T_{J}$  = 25°C

Figure 23. Clamped inductive switching energies vs. snubber capacitance  $C_S$  at  $V_{DS}$  = 800V,  $I_D$  = 20A, and  $T_1$  = 25°C

Figure 22. RC snubber energy loss vs.  $R_{G,EXT}$  at  $V_{DS}$  = 800V,  $I_D$  = 20A, and  $T_J$  = 25°C

Figure 24. RC snubber energy losses vs. snubber capacitance  $C_S$  at  $V_{DS}$  = 800V,  $I_D$  = 20A, and  $T_J$  = 25°C

Figure 25. Clamped inductive switching energy vs. junction temperature at  $V_{DS}$  = 800V and  $I_D$  =20A

Figure 26. Schematic of the half-bridge mode switching test circuit with device RC snubbers ( $R_s$  = 20 $\Omega$ ,  $C_s$  = 100pF) and a bus RC snubber ( $R_{SS}$  = 2.5 $\Omega$ ,  $C_{SS}$ =100nF).

## **Applications Information**

SiC FETs are enhancement-mode power switches formed by a high-voltage SiC depletion-mode JFET and a low-voltage silicon MOSFET connected in series. The silicon MOSFET serves as the control unit while the SiC JFET provides high voltage blocking in the off state. This combination of devices in a single package provides compatibility with standard gate drivers and offers superior performance in terms of low on-resistance ( $R_{DS(on)}$ ), output capacitance ( $C_{oss}$ ), gate charge ( $Q_G$ ), and reverse recovery charge ( $Q_G$ ) leading to low conduction and switching losses. The SiC FETs also provide excellent reverse conduction capability eliminating the need for an external anti-parallel diode.

Like other high performance power switches, proper PCB layout design to minimize circuit parasitics is strongly recommended due to the high dv/dt and di/dt rates. An external gate resistor is recommended when the FET is working in the diode mode in order to achieve the optimum reverse recovery performance. For more information on SiC FET operation, see https://www.qorvo.com/design-hub.

A snubber circuit with a small  $R_{(G)}$ , or gate resistor, provides better EMI suppression with higher efficiency compared to using a high  $R_{(G)}$  value. There is no extra gate delay time when using the snubber circuitry, and a small  $R_{(G)}$  will better control both the turn-off  $V_{(DS)}$  peak spike and ringing duration, while a high  $R_{(G)}$  will damp the peak spike but result in a longer delay time. In addition, the total switching loss when using a snubber circuit is less than using high  $R_{(G)}$ , while greatly reducing  $E_{(OFF)}$  from mid-to-full load range with only a small increase in  $E_{(ON)}$ . Efficiency will therefore improve with higher load current. For more information on how a snubber circuit will improve overall system performance, visit the Qorvo website at https://www.qorvo.com/design-hub.

## Important notice

The information contained herein is believed to be reliable; however, Qorvo makes no warranties regarding the information contained herein and assumes no responsibility or liability whatsoever for the use of the information contained herein. All information contained herein is subject to change without notice. Customers should obtain and verify the latest relevant information before placing orders for Qorvo products. The information contained herein or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regard to such information itself or anything described by such information. THIS INFORMATION DOES NOT CONSTITUTE A WARRANTY WITH RESPECT TO THE PRODUCTS DESCRIBED HEREIN, AND QORVO HEREBY DISCLAIMS ANY AND ALL WARRANTIES WITH RESPECT TO SUCH PRODUCTS WHETHER EXPRESS OR IMPLIED BY LAW, COURSE OF DEALING, COURSE OF PERFORMANCE, USAGE OF TRADE OR OTHERWISE, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Without limiting the generality of the foregoing, Qorvo products are not warranted or authorized for use as critical components in medical, life-saving, or life-sustaining applications, or other applications where a failure would reasonably be expected to cause severe personal injury or death.

| TO263-7L (D2PAK-7L) PACKAGE OUTLINE, MARKING, TAPE AND REEL SPECIFICATION | PART | Page <b>1</b> of <b>4</b> |

|---------------------------------------------------------------------------|------|---------------------------|

| DS TO 263 71                                                              |      | Rev D                     |

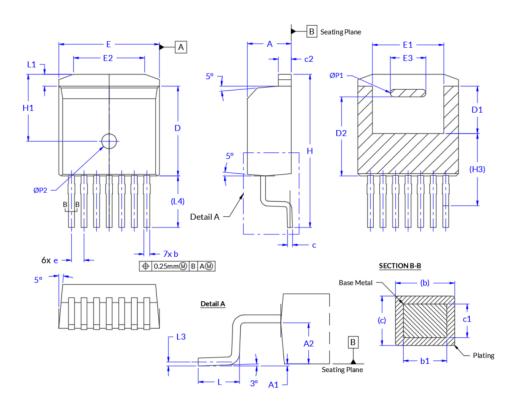

### **PACKAGE OUTLINE**

|       | 7L-D2PAK |       |          |      |  |

|-------|----------|-------|----------|------|--|

| SYM   | М        | М     | IN       | CH   |  |

| 31141 | Min      | Max   | Min      | Max  |  |

| Α     | 4.30     | 4.56  | .169     | .180 |  |

| A1    | 0.00     | 0.25  | .000     | .010 |  |

| A2    | 2.45     | 2.75  | .096     | .108 |  |

| b     | 0.50     | 0.70  | .020     | .028 |  |

| b1    | 0.50     | -     | .020     | -    |  |

| С     | 0.40     | 0.60  | .016     | .024 |  |

| c1    | 0.40     |       | .016     |      |  |

| c2    | 1.20     | 1.40  | .047     | .055 |  |

| D     | 8.93     | 9.23  | .352     | .363 |  |

| D1    | 4.65     | 4.95  | .183     | .195 |  |

| D2    | 7.90     | 8.10  | .311     | .319 |  |

| e     | 1.27     | BSC   | .050 BSC |      |  |

| E     | 10.08    | 10.28 | .397     | .405 |  |

| E1    | 6.82     | 7.62  | .269     | .300 |  |

| E2    | 6.50     | 8.60  | .256     | .339 |  |

| E3    | 3.50     | 3.70  | .138     | .146 |  |

| Н     | 15.00    | 16.00 | .591     | .630 |  |

| H1    | 6.68     | 6.88  | .263     | .271 |  |

| H3    | 7.31     | REF.  | .287     | REF  |  |

| L     | 1.90     | 2.50  | .075     | .098 |  |

| L1    | 0.98     | 1.42  | .039     | .056 |  |

| L3    | 0.25     | BSC   | .0098    | BSC  |  |

| L4    | 5.22     | REF   | .205     | REF  |  |

| ØP1   | 0.65     | 0.85  | .026     | .033 |  |

| ØP2   | 1.40     | 1.60  | .055     | .063 |  |

### Notes:

- 1. GENERAL TOLERANCE: ±0.1 unless otherwise specified

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. PACKAGE BODY SIDES EXCLUDE MOLD FLASH AND GATE BURRS.

- 4. DIMENSION LIS MEASURED IN GAUGE LINE.

- 5. CONVERTED INCH DIMENSIONS ARE NOT NECESSARILY EXACT.

- 6. DIMENSION c1 AND b1 APPLIES TO BASE METAL ONLY

| TO263-7L (D2PAK-7L) PACKAGE OUTLINE, PART MARKING, TAPE AND REEL SPECIFICATION | Page <b>2</b> of <b>4</b> |

|--------------------------------------------------------------------------------|---------------------------|

| DS_TO_263_7L                                                                   | Rev D                     |

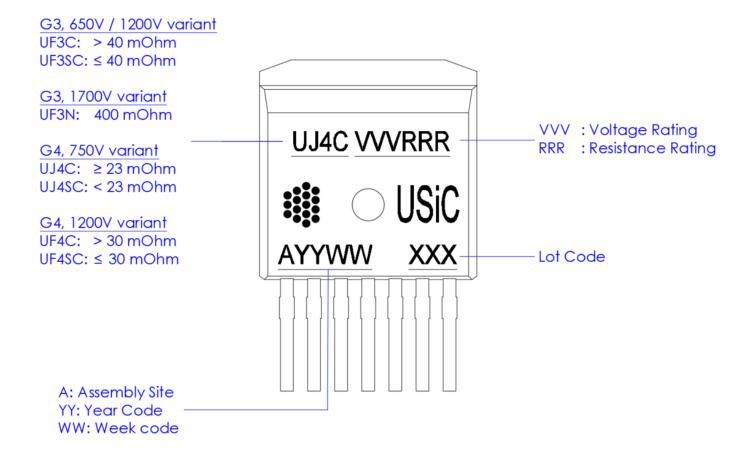

#### **PART MARKING**

Template: FOR-000530 Rev G

| TO263-7L | (D2PAK-7L)  | PACKAGE            | OUTLINE, | PART |

|----------|-------------|--------------------|----------|------|

| MARKING, | TAPE AND RE | <b>EL SPECIFIC</b> | ATION    |      |

TO 000 7

Page **3** of **4**

Rev D

DS\_TO\_263\_7L

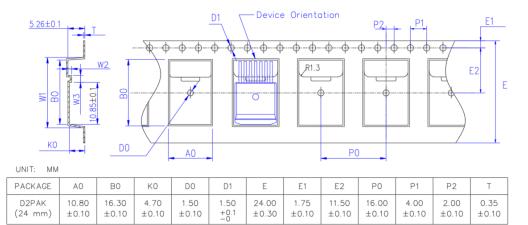

## **PACKING TYPE**

## Carrier Tape

| Ext    | erior | size     |            |

|--------|-------|----------|------------|

|        | W1    | 16.9±0.1 |            |

| Spec   | W2    | 1.3±0.1  |            |

| '      | W3    | 1.0±0.1  |            |

|        | W1    | 17.2±0.1 | (1)        |

| Spec 2 | W2    | 1.8±0.1  | <b>(b)</b> |

|        | W3    | 0.85±0.1 | 0          |

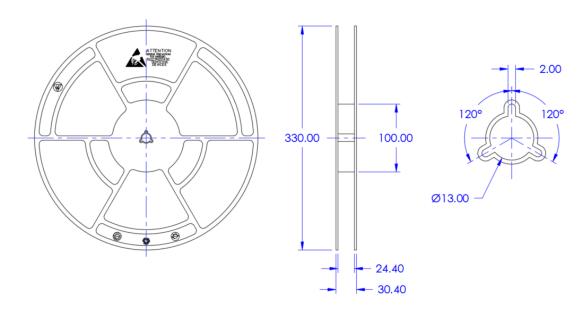

## Reel

All dimensions in millimeters Anti-Static Tape and Rell (T&R) Quantity per Reel: 800 units

#### **DISCLAIMER**

The information contained herein is believed to be reliable; however, Qorvo makes no warranties regarding the information contained herein and assumes no responsibility or liability whatsoever for the use of the information contained herein. All information contained herein is subject to change without notice. Customers should obtain and verify the latest relevant information before placing orders for Qorvo products. The information contained herein, or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regards to such information itself or anything described by such information. THIS INFORMATION DOES NOT CONSTITUTE A WARRANTY WITH RESPECT TO THE PRODUCTS DESCRIBED HEREIN, AND QORVO HEREBY DISCLAIMS ANY AND ALL WARRANTIES WITH RESPECT TO SUCH PRODUCTS WHETHER EXPRESS OR IMPLIED BY LAW, COURSE OF DEALING, COURSE OF PERFORMANCE, USAGE OF TRADE OR OTHERWISE, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Without limiting the generality of the foregoing, Qorvo products are not warranted or authorized for use as critical components in medical, lifesaving, or life-sustaining applications, or other applications where a failure would reasonably be expected to cause severe personal injury or death.

### **REVISION HISTORY**

| Revision | Create Date (mm/dd/yyyy) | Description of Change                                                                   | Initiator of<br>Change |

|----------|--------------------------|-----------------------------------------------------------------------------------------|------------------------|

| С        | 11/06/2023               | Updated to Qorvo template Updated Package outline drawing based latest drawing revision | Glenn Galang           |

| D        | 05/21/2024               | Added illustration of device orientation on carrier tape (page 3)                       | Glenn Galang           |

|          |                          |                                                                                         |                        |

|          |                          |                                                                                         |                        |

|          |                          |                                                                                         |                        |

|          |                          |                                                                                         |                        |

|          |                          |                                                                                         |                        |

|          |                          |                                                                                         |                        |

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales