LDO PSRRの連載記事パートIVでは、PSRRとは?パートIII と題する前回のブログに続き、LDOの動作および興味深いパラメータに関して説明します。以前のブログも簡単にご覧ください。本記事では、現実的視点から電源電圧変動除去比(PSRR)に焦点を絞ります。データシートの数値とオシロスコープの計測値を照合すると理解しやすくなります。

まず、複数のロードポイントが存在するあらゆる電子システムでは(リニア・レギュレータのみを備えていても)、出力電圧リップルが発生し、他の部品に影響を与えうるとういことを述べておきます。では、PSRR に関して実際のオシロスコープ計測値を使用して説明しましょう。

データシートに示されている PSRR は、入力と出力の電圧リップルの比率として測定されています。測定そのものは、いくつかの規則を覚えておくと比較的簡単です。 LDO (低ドロップアウト) レギュレータには、正弦波のリップル電圧が結合されたクリーンな直流電源から電力供給する必要があります。出力負荷は、電子負荷と LDO レギュレータの相互作用を防ぐために、厳密な抵抗がなければなりません。リップル電圧の振幅は、LDO を制御し、十分な電圧ヘッドルームを確保するために、慎重に選ぶ必要があります。たとえば、VIN=3.6 V および VOUT=3.3 V の場合、AC 信号の振幅を 300 mV にすることはできません。というのは、 LDO はドロップアウト状態になり、入力リップルをそのまま出力してしまうからです。

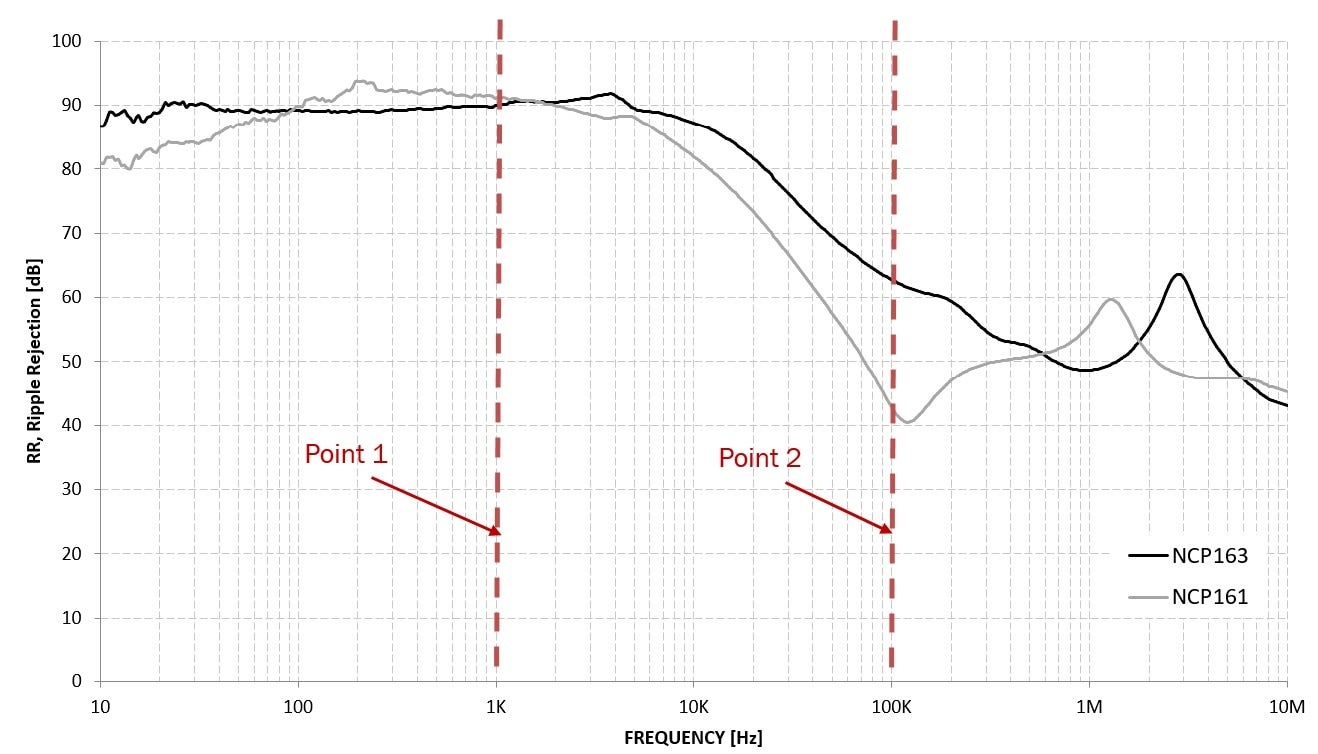

たとえば、図1は、オン・セミコンダクターの LDO 「NCP163 」と「NCP161」の PSRR チャートを示しています。同様のチャートは、半導体業界全体で多くのLDOデータシートにて幅広く使用されています。実際の例では、最大10 MHzまでの周波数範囲における PSRR を示しています。当社の事例では、以下の図で示すように、1 kHz と 100 kHz の2つの時間領域のポイントをマークしています。 1 kHz は、データシートの電気特性表において PSRR の仕様として最も一般的な周波数であり、100 kHz は、多くのDC-DCコンバータが動作する領域です。

図1. NCP163 および NCP161 デバイスの PSRR チャート

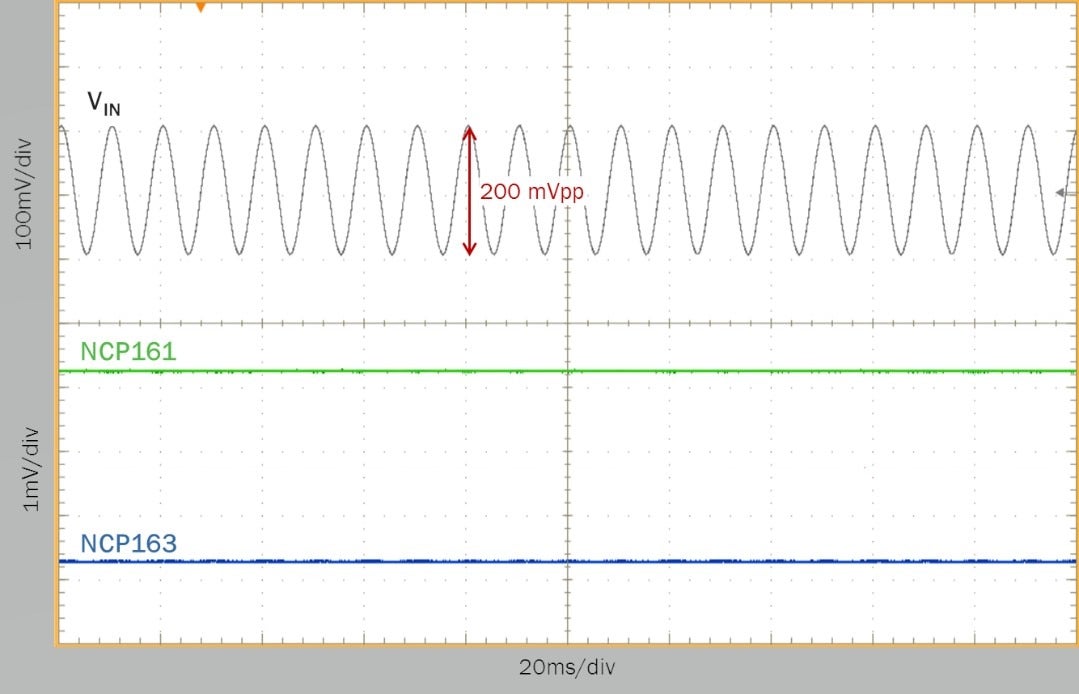

ポイント1では、PSRR が約 90 dB で、入力リップルが約 32,000 倍に減衰されていることがわかります。 下の図は、入力電圧リップル 200 mVpp で撮像したものです。これは、LDO出力のリップルがわずか 6 uV であり、オシロスコープでは確認できません。図2 に示すように直線になっています。

図2. 1 kHz のオシロスコープ図: 両デバイスの PSRR は約 90 dB

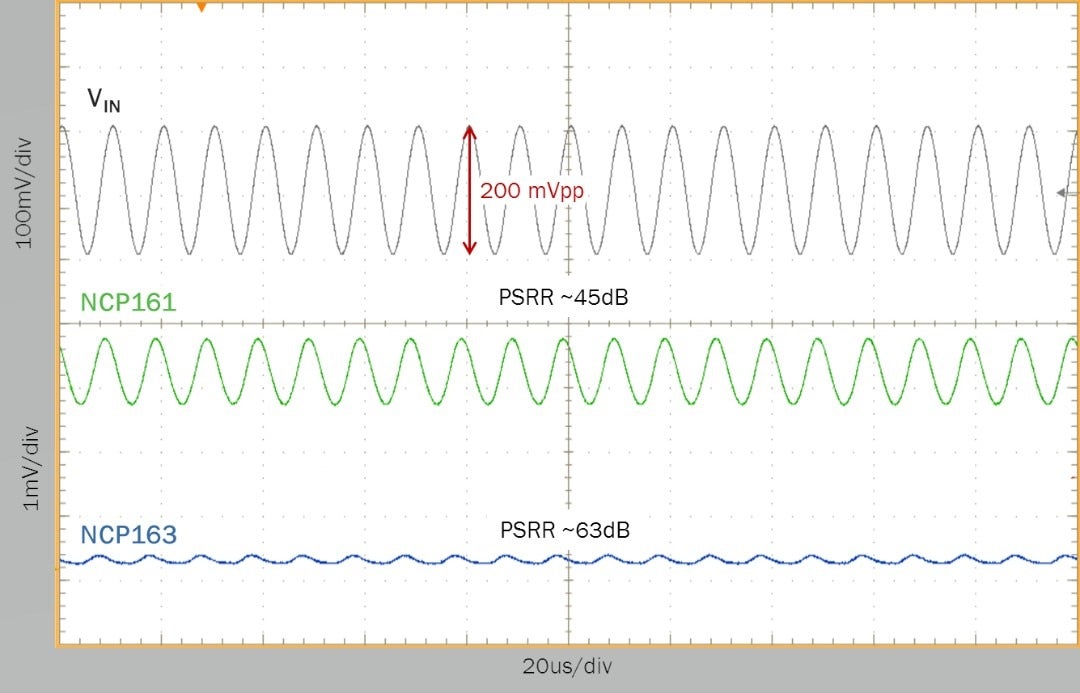

図3は、100 kHz 周波数で起きている状況を示しています。図1を見ると、両デバイスにおいてPSRRが90 dBよりはるかに低く、両者のあいだに大きな違いがあることが分かります。時間領域を細かく見ると、たとえば、アプリケーションが 1 mVpp より小さな入力電圧リップルを必要としているとします。NCP161はボーダーラインにあるのに対し、NCP163は大きなマージンを持って要件を満たしており、ピーク・トゥ・ピークでリップルは 200 uVpp を下回っています。

図3. 100 kHz のオシロスコープ図: PSRRが大きく異なる

図1~3が示すように、PSRRパラメータは、電気的な表における 1 つの数値としてだけでは、設計されたアプリケーションにおける適性を判断するために十分ではありません。システムエンジニアは、入力電圧のリップル周波数を考慮し、必要なポイントで PSRR チャートをチェックしなければなりません。 MHz 領域でスイッチングする今日の DC-DC コンバータと LDO は、最適な性能を実現するために慎重にマッチさせる必要があります。ほとんどの LDO データシートでは、わずか 1 kHz で PSRR を規定し、良好な性能を得るために高い値を推奨していますが、より高い周波数範囲では性能が低いため、DC-DC ポストレギュレータとしては十分でないかもしれません。この理由により、アプリケーションの条件を考慮して、適切な LDO を選ぶことが非常に重要です。オン・セミコンダクターは、お客さまが設計に必要な情報を入手できるように、すべてのデータシートで図1と同様のチャートを示しています。

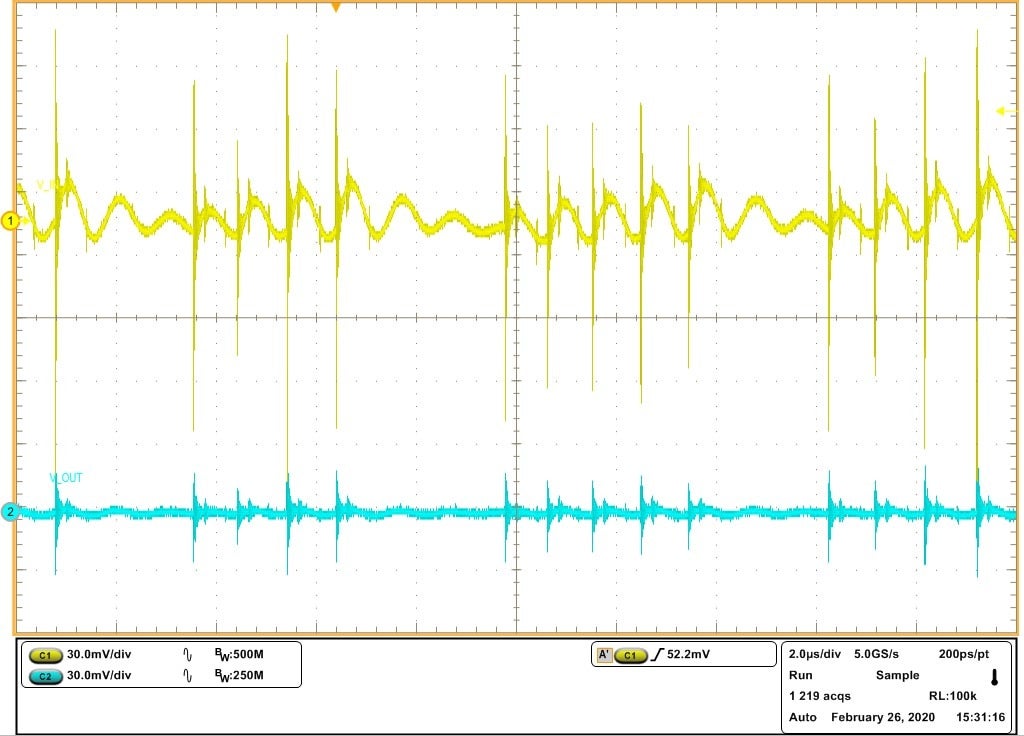

最後に、DC-DC コンバータと LD Oの組み合わせが、システムソリューションとしてどのように機能するかを見ていきましょう。 DC-DC コンバータとして「FAN2356」を採用しました。最大 96% の効率性と最大 1.5 MHz のスイッチング周波数を調整可能です。この例では、スイッチング周波数が 500 kHz に設定されています。ポストレギュレータ LDOは「NCP163」で、これは超低ノイズ出力の高 PSRR LDOです。 DC-DC コンバータの出力電圧は 3.6 V 、LDO 出力は 3.3 V です。これに基づいて、電圧のヘッドルームは 300 mV であり、LDO 負荷電流は 250 mA です。図4では、黄色のトレースで DC-DC 出力電圧を、青色のトレースで LDO 出力電圧を確認できます。縦軸は、両トレースに関して30 mV/div に設定されており、LDOの影響を容易に比較できます。

図4. LDO ポストレギュレータを備えた DC-DC コンバータ

DC-DC 出力において大きなスパイクおよびリップル電圧が生じていることが明らかに分かります。これは、電力の影響を受けやすいデバイスで問題を起こす可能性があります。 LDO 出力は、よりクリアで安定しています。リップルは mV の範囲まで抑えられ、スパイクは最大 30 ~ 40 mV まで抑えられています。このような性能を活かし、LDO の出力電圧は、電力の影響を受けやすい幅広いアプリケーションの電源として使用できます。

オン・セミコンダクターのブログを読者登録し、ソーシャルメディアで当社をフォローして、

最新のテクノロジ、ソリューション、企業ニュースを入手してください!

Twitter | Facebook | LinkedIn | Instagram | YouTube